ISSN: 2454-132X Impact factor: 4.295 (Volume 5, Issue 3)

Available online at: www.ijariit.com

# Artificial Neural Network architecture and hardware Chip Implementation using VHDL

Km Manisha

manishakattariya@gmail.com

S. D. College of Engineering and Technology,

Muzaffarnagar, Uttar Pradesh

Dr. A. K. Gautam

<u>kattariyaec123@gmail.com</u>

S. D. College of Engineering and Technology,

Muzaffarnagar, Uttar Pradesh

#### **ABSTRACT**

Artificial neural networks are extended on the basis of brain structure. Like the brain, ANNs can recognize patterns, handle facts and figures and be trained. They are prepared by artificial neurons which employ the quintessence of genetic neurons. In the research work, we have considered the 8 inputs ANN signal which is multiplied with their corresponding weights. The hardware chip is designed to support the system functionality in Xilinx ISE 14.2 software. The designed chip is simulated with Modelsim 10.0 software for test cases. The designed chip is also synthesized on SPARTAN-3E FPGA using VHDL programming and device hardware and timing parameters are also analyzed for the functionality of the chip. Keywords: Artificial Neural Network (ANN), FPGA, Xilinx ISE software.

Keywords— Artificial Neural Network (ANN), FPGA, Xilinx ISE software

# 1. INTRODUCTION

An ANN [1, 2] is based on a gathering of connected units or nodes called artificial neurons which loosely model the neurons in a biological brain. Each connection, like the synapses in a biological brain, can transmit a signal from one artificial neuron to another. An artificial neuron [3, 4] that receives a signal can process it and then signal supplementary artificial neurons connected to it. In general ANN implementations, the signal at a connection between artificial neurons is a real number, and the output of each artificial neuron is computed by some non-linear function of the sum of its inputs. The connections between artificial neurons are called 'edges'. Artificial neurons and edges typically have weights [5, 6] that adjust as knowledge proceeds. The weight increases or decreases the strength of the signal at a connection. Artificial neurons [3, 7] may have a threshold such that the signal is only sent if the aggregate signal crosses that threshold. Typically, artificial neurons are aggregated into layers. Different layers may perform different kinds of transformations on their inputs. Signals travel from the first layer (the input layer) to the last layer (the output layer), possibly after traversing the layers multiple times.

The main objective of the ANN-based approach is to solve the real problems as the human brain is cable to solve. However, the computations will involve the functioning of specific tasks, leading to the deviations from biology. The artificial neural networks are applied for the different variability of tasks, including machine learning [10], computer vision, social networks, video games, network filtering, computer vision, speed recognition, machine translation, speech recognition, filtering, social network and medical applications.

#### 1.2 ANN architecture

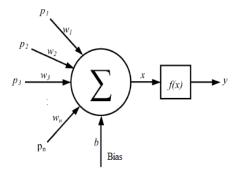

Fig. 1: Neuron structure

# Manisha Km, Gautam A. K.; International Journal of Advance Research, Ideas and Innovations in Technology

The general model of the neural network is shown in figure 1. It has the 'n' number of inputs. Let us consider that the inputs are  $p_1, p_2, p_3, \dots, p_n$ . These inputs are processed with their corresponding weights as  $w_1, w_2, w_3, \dots, w_n$  and 'b' is the bias input. The nonlinear execution function [8, 9] is f(x). Neuron processing is expressed with the help of the equation.

$$y = f(x) \tag{1}$$

$$x = \sum_{i=1}^{n} p_i w_i + Bias(b)$$

(2)

The  $w_i$  is referred to as the weights for the  $i^{th}$  connections and b is the bias inputs. The behavior of the function f(x) is the nonlinear excitation function. The most popular excitation function used is expressed as

$$f(x) = x \tag{3}$$

For log sigmoid function,

$$f(x) = \frac{1}{1 + e^{-x}} \tag{4}$$

For tansigmoid function,

$$f(x) = \frac{e^x - e^{-x}}{e^x + e^{-x}} \tag{5}$$

### 2. RESULTS AND DISCUSSIONS

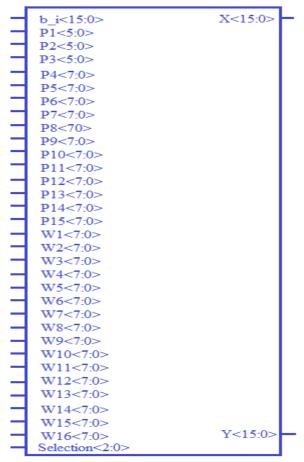

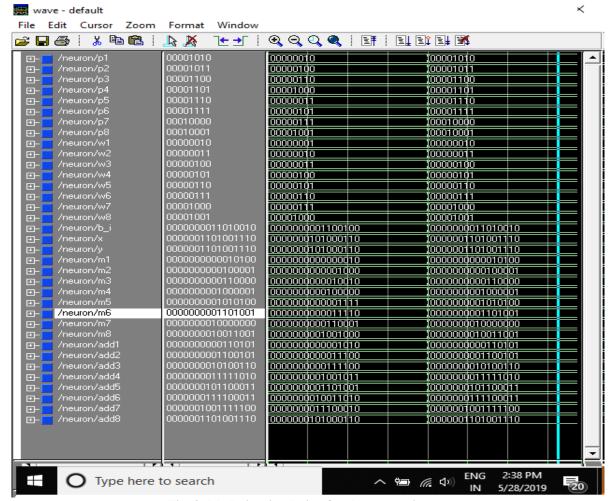

The Xilinx software simulation results for 8 input ANN Architecture is shown in figure 2 that presents the RTL level view of the developed chip. The RTL provides the details of all the pins used for the design of the chip. The Modelsim simulation result is shown in figure 3 that presents the simulation output of two test cases.

#### 2.1 Test-1

P1<7:0> = "00000010" in binary =2 in decimal, P2<7:0>"00000100" in binary = 4 in decimal, P3<7:0> = "00000110" in binary =6 in decimal, P4<7:0> = "00001000" = 8 in decimal, P5<7:0> = "00000011" in binary = 3 in decimal, P6<7:0> = 00000101" in binary = 5 in decimal, P7<7:0> = "00000111" in binary = 7 in decimal, P8<7:0> = "00001001" in binary =9 in decimal, W1<7:0> = "00000001" in binary =1 in decimal, W2<7:0> = "00000010" in binary =2 in decimal W3<7:0> = "00000011" in binary = 3 in decimal, W4<7:0> = "00000100" in binary =4 in decimal, W5<7:0> = "00000101" = 5 in decimal, W6<7:0> = "00000110" in binary =6 in decimal, W7<7:0> = "00000101" in binary = 7 in decimal, W8<7:0> = "00001000" = 8 in decimal, b\_i<15:0> = "0000000001100100" = 100 in decimal, selection\_input = "000" Then output will be Y<15:0> = "0000000011000110" = 326 in decimal.

Fig. 2: RTL View of 16-Point ANN architecture chip

Fig. 3: Modesim simulation for the neuron inputs

# 2.2 Test-2

P9<7:0> = "00001010" in binary =10 in decimal, P10<7:0> "00001011" in binary = 11 in decimal, P11<7:0> = "00001100" in binary =12 in decimal, P12<7:0> = "00001101" = 13 in decimal, P13<7:0> = "00001110" in binary =14 in decimal, P14<7:0> = 00001111" in binary =15 in decimal, P15<7:0> = "00010000" in binary = 16 in decimal, P16<7:0> = "00010001" in binary =17 in decimal, W9<7:0> = "00000010" in binary =2 in decimal, W10<7:0> = "00000011" in binary = 3 in decimal, W11<7:0> = "00000110" in binary =6 in decimal, W12<7:0> = "00000101" in binary =6 in decimal, W14<7:0> = "00000101" in binary =7 in decimal, W15<7:0> = "00001000" = 8 in decimal, W16<7:0> = "00001001" = 9 in decimal, b\_i<15:0> = "0000000011110" = 210 in decimal, selection\_input = "001". Then output will be Y <15:0> = "0000001101001110" = 846 in decimal.

## 3. XILINX DEVICE UTILIZATION SUMMARY

Xilinx is one of the largest manufacturers of FPGA and ASIC based solutions. Xilinx has become the semiconductor industry leader in business targets, market coverage of the forefront of technology. In the Xilinx, the designer can develop the code using any HDL programming language such as VHDL or Verilog HDL. After that, the design is checked and functionality simulated in the Xilinx. In this tool, the chip is designed to design and its Register Transfer Logic (RTL) view and schematic can be seen. It is a tool used to test the code on the FPGA platform with different test benches. The tool provides complete information of simulation, synthesis, and timing analysis. The pre-synthesis parameters can be extracted from the tool such as hardware parameters, timing parameters and memory utilization etc. The percentage of hardware that is used by the device is given by the device utilization report for the implementation of chip. Device hardware includes No. of slices. Of input LUTs, No. of bounded IOBs and No. of Gated Clocks (GCLKs) used in design implementation. Timing details provides the knowledge of the maximum frequency and combinational delay. To complete the design, the total memory utilization required is also given. The Xilinx software gives the details of the hardware utilization for 8 input ANN. Table 1 presents the utilization report of the hardware parameters and table 2 presents the timing results.

Table 1: Hardware summary for 16 input ANN for SPARTAN 3E FPGA

| ANN (16 input) |

|----------------|

| 710            |

| 524            |

| 1025           |

| 181            |

| 1              |

| 121518 Kb      |

|                |

## Manisha Km, Gautam A. K.; International Journal of Advance Research, Ideas and Innovations in Technology

Table 2: Timing Parameters for 16 input ANN for SPARTAN-3E, FPGA

| Parameter                         | ANN (16 input) |

|-----------------------------------|----------------|

| Frequency (MHz)                   | 235 MHz        |

| Min Period (ns)                   | 2.417          |

| Min time before clock signal (ns) | 3.240          |

| Max Time after clock signal(ns)   | 6.290          |

| Combinational Delay (ns)          | 9.120          |

#### 4. CONCLUSION

A neural network is produced by a sequence of nodes called neurons that are structured in layers. Each neuron in a layer is associated with each neuron in the next layer through a weighted relationship. The hardware chip of 16 input ANN architecture is designed in Xilinx ISE 14.2 software successfully and simulated in Modalism 10.0 software. The designed chip is synthesized on SPARTAN-3E FPGA. The designed chip support the frequency of 235 MHz. The timing detail parameters are a minimum period (ns), the minimum time before clock signal (ns), maximum time after clock signal (ns) and combinational delay (ns) which are estimated as 2.417 ns, 3.240 ns, 6.290 ns and 9.120 ns respectively.

## 5. REFERENCES

- [1] Acharya, U. R., Bhat, P. S., Iyengar, S. S., Rao, A., and Dua, S. (2003). Classification of heart rate data using artificial neural network and fuzzy equivalence relation. Pattern Recognition, 36(1), 61-68.

- [2] Bose, B. K. (2007). Neural network applications in power electronics and motor drives- an introduction and perspective. IEEE Transactions on Industrial Electronics, 54(1), 14-33.

- [3] Gharehbaghi, A., Sepehri, A. A., and Babic, A. (2019, May). Forth Heart Sound Detection Using Backward Time-Growing Neural Network. In International Conference on Medical and Biological Engineering (pp. 341-345). Springer, Cham.

- [4] Himavathi, S., Anitha, D., and Muthuramalingam, A. (2007). Feedforward neural network implementation in FPGA using layer multiplexing for effective resource utilization. IEEE Transactions on Neural Networks, 18(3), 880-888.

- [5] Kalyan, K., Jakhia, B., Lele, R. D., Joshi, M., and Chowdhary, A. (2014). Artificial neural network application in the diagnosis of disease conditions with liver ultrasound images. Advances in bioinformatics, 2014.

- [6] Maeda, Y., and Wakamura, M. (2005). A simultaneous perturbation learning rule for recurrent neural networks and its FPGA implementation. IEEE Transactions on Neural Networks, 16(6), 1664-1672.

- [7] Mukhopadhyay, I., and Chakraborty, M. (2014). Hardware Realization of Artificial Neural Network Based Intrusion Detection and Prevention System. Journal of Information Security, 5(04), 154.

- [8] Patil, S., Saxena, A., Talreja, T., and Bhatti, V. (2019). Medical Diagnosis of Ailments through Supervised Learning Techniques on Sounds of the Heart and Lungs. In Soft Computing and Signal Processing (pp. 253-262). Springer, Singapore.

- [9] Patidar, S., Pachori, R. B., and Acharya, U. R. (2015). Automated diagnosis of coronary artery disease using tunable-Q wavelet transform applied on heart rate signals. Knowledge-Based Systems, 82, 1-10.

- [10] Shi, W. Y., and Chiao, J. C. (2018). Neural network based real-time heart sound monitor using a wireless wearable wrist sensor. Analog Integrated Circuits and Signal Processing, 94(3), 383-393.