ISSN: 2454-132X Impact factor: 4.295 (Volume3, Issue1)

Available online at: www.ijariit.com

# Design & Performance Analysis of Instrumentation Amplifier at Nanoscale

#### Dr. M. Nizamuddin

Assistant professor, Ece Deptt., BGSB University, Rajouri, J&K nizamdelhi25@gmail.com

Abstract:- In this research work, simulation and comparative analysis of Instrumentation Amplifier at different voltages. DC voltage gain is 133.4 dB, average power is 589 mW, bandwidth is 3.87 MHz have been computed using HSPICE Software at 0.5V. DC voltage gain is 77.84 dB, average power is 290mW, bandwidth is 164MHz have been computed using HSPICE Software at 1.5V. The proposed Instrumentation is efficient in medical applications due to high gain and high bandwidth. Instrumentation Amplifier based on CMOS has been designed and simulated using 32nm CMOS technology. In this design, care has been taken in selection of the values to maintaining the gain and bandwidth of the Instrumentation Amplifier.

Keywords – Instrumentation Amplifier, CMOS technology, Low voltage, Low power, Output resistance, Bandwidth. DC Gain.

## I. INTRODUCTION

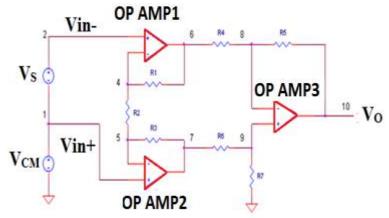

Instrumentation amplifiers are actually made up of 2 parts: a buffered amplifier using OP AMP1, OP AMP2 and a basic differential amplifier OP AMP3. The differential amplifier part is often essential when measuring sensors. A sensor produces a signal between its terminals. However, for some applications, neither terminal may be connected to the same ground potential as your measuring circuit. The terminals may be biased at a high potential or riding on a noise voltage. The differential amplifier rescues the signal by directly measuring the difference between the sensor's terminals.

The buffered amplifier OP AMP1 and OP AMP2 not only provides gain, but prevents the sensor resistance from affecting the resistors in the op amp circuit, and vice-versa. The realization of high speed and high accuracy Instrumentation Amplifier has proven. Optimizing the circuit design for both requirements leads to conflicting demands. The realization of high speed and high accuracy opamps has proven to be very challenging task. Optimizing the circuit design for both requirements leads to conflicting demands [1]. A single-stage folded cascode topology is a popular approach in designing high speed op-amps. Besides large unity gain frequency, it offers large output swing. However, it has limitation to provide high DC gain which is required for high settling accuracy. In 1990, Bult and Geelen proposed the folded cascode op-amp with gain boosting technique [3]. This technique help to increase the op-amp DC gain without sacrificing the output swing of a regular cascade structure [3]. The pushing up the doublet can raise stability problem [5], [6].

Advantages of Three Op-amp Instrumentation Amplifier

- The gain of a three op-amp instrumentation amplifier circuit can be easily varied and controlled by adjusting the value of Rgain without changing the circuit structure.

- The gain of the amplifier depends only on the external resistors used. Hence, it is easy to set the gain accurately by choosing the resistor values carefully.

- The input impedance of the instrumentation amplifier is dependent on the non-inverting amplifier circuits in the input stage. The input impedance of a non-inverting amplifier is very high.

- The output impedance of the instrumentation amplifier is the output impedance of the difference amplifier, which is very low

- The CMRR of the op-amp 3 is very high and almost all of the common mode signal will be rejected.

Figure.1-Proposed Instrumentation Amplifier

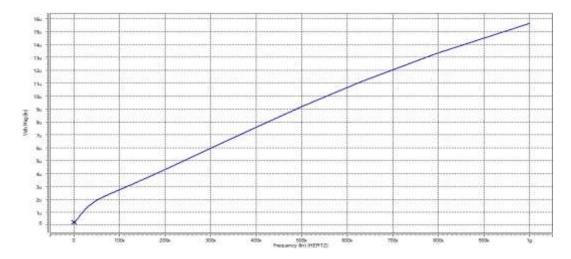

## Simulated Data of Proposed Instrumentation Amplifier at 1.5 V

Figure.2-Average Power of Proposed Instrumentation Amplifier at 1.5V

Figure 3-Output Signal of OP AMP1 of Proposed Instrumentation Amplifier at 1.5

Figure 4-Output Signal of OP AMP2 of Proposed Instrumentation Amplifier at 1.5V

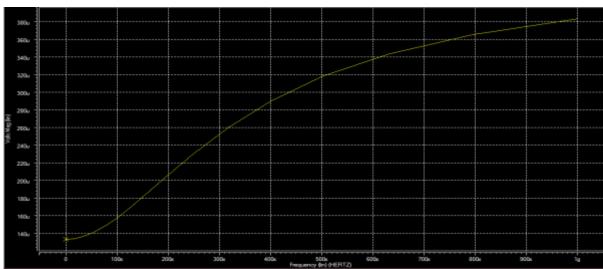

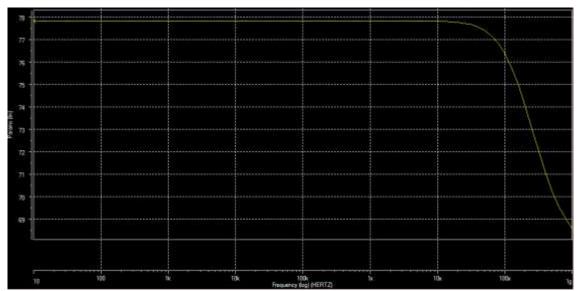

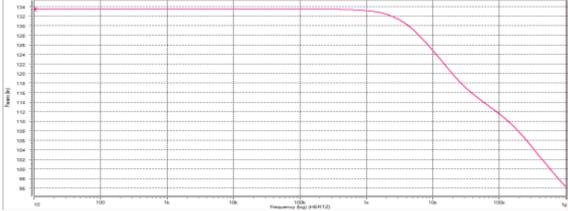

Figure 5-DC Gain of Proposed Instrumentation Amplifier at 1.5V

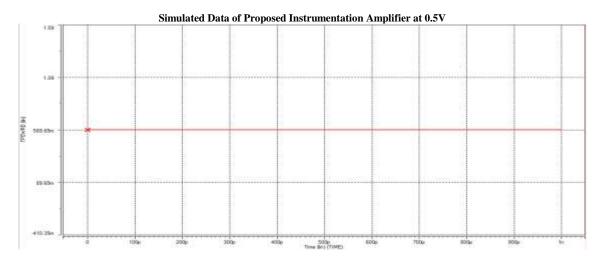

Figure 6-Average Power of Proposed Instrumentation Amplifier at  $0.5\mathrm{V}$

Figure 7-Output Signal of OP AMP1 of Proposed Instrumentation Amplifier at 0.5V

Figure 8-Output Signal of OP AMP2 of Proposed Instrumentation Amplifier at  $0.5\mathrm{V}$

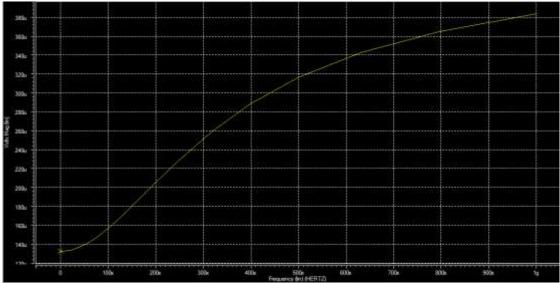

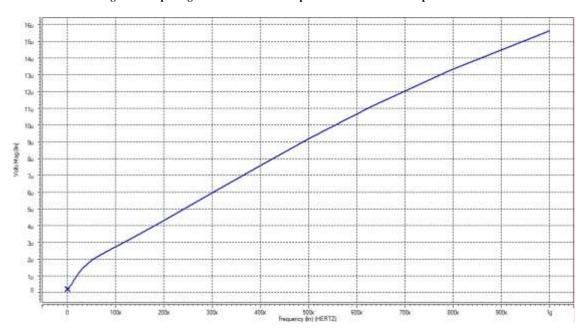

Figure 9-DC Gain of Proposed Instrumentation Amplifier at 0.5V

Table 1: Comparative analysis of Instrumentation Amplifier at different voltages using 32 nm tech. node.

| S. No. | Parameters      | Instrumentation<br>Amplifier at 0.5V | Instrumentation<br>Amplifier at 1.5V |

|--------|-----------------|--------------------------------------|--------------------------------------|

| 1      | DC GAIN         | 133.4 dB                             | 77.84 dB                             |

| 2      | 3- dB Bandwidth | 3.87 MHz                             | 164MHz                               |

| 3      | Average Power   | 589 mW                               | 290mW                                |

Table 2: Parameters used in the proposed Instrumentation Amplifier

| S. No. | Parameters                       | Value                        |

|--------|----------------------------------|------------------------------|

| 1      | Channel Length                   | 32nm                         |

| 2      | Channel Width                    | 763nm                        |

| 3      | Supply Voltages                  | 0.5V and 1.5V                |

| 4      | NMOS TRANSISTORS                 | 39                           |

| 5      | PMOS TRANSISTORS                 | 27                           |

| 6      | Number of Operational Amplifiers | 03                           |

| 7      | Technology File                  | PTM 32nm Metal Gate / High-K |

#### CONCLUSION

In this research work, simulation and comparative analysis of Instrumentation Amplifier at different voltages. DC voltage gain, average power, bandwidth etc have been computed using HSPICE Software. The proposed Instrumentation is efficient in medical applications due to high gain and high bandwidth. Instrumentation Amplifier based on CMOS has been designed and simulated using 32nm CMOS technology.

### REFERENCES

- 1 R. R. Harrison and C. Charles, "A low-power low-noise CMOS amplifier for neural recording applications," IEEE Journal of Solid-State Circuits, vol. 38, pp. 958-965, 2003.

- 2 M. S. J. Steyaert and W. M. C. Sansen, "A micropower low-noise monolithic instrumentation amplifier for medical purposes," IEEE Journal of Solid-State Circuits, vol. 22, pp. 1163-1168, 1987.

- 3 R. F. Yazicioglu, P. Merken, R. Puers, and C. Van Hoof, "A 60 uW 60nV/ Hz readout front-end for portable biopotential acquisition systems," IEEE Journal of Solid-State Circuits, vol. 42, pp. 1100-1110, 2007.

- 4 Chih-Jen Yen, Wen-Yaw Chung and Mely Chen Chi. "Micro-Power Low Offset Instrumentation Amplifier IC Design For Bio-Medical System Applications". IEEE Transactions On Circuits And Systems-I: Regular Papers. 2004; 51(4): 691-699.

- 5 Yasin FM, Yap MT, and Reaz MBI. "CMOS Instrumentation Amplifier with Offset Cancellation Circuitry for Biomedical Applications". In Proc. of 5th WSEAS. 2006, Spain, pp 168-171.

- 6 Silveira F, Flandre D, Jespers PGA. A gm/ID based methodology for the design of CMOS analog circuit and its application to the synthesis of a silicon-ion- insulator micropower OTA. IEEE Journal of Solid State Circuits. 1996; 31: 1314-1319.

- 7 Manish Goswami. and Smriti Khanna. "DC Suppressed High Gain Active CMOS Instrumentation Amplifier for Biomedical Application". In Proc. IEEE Inter. Symp. on Circuits and Systems (ISCAS'04). Vol 4, pp. 9-12.

- 8 MSJ Steyaert, WMC Sansen and C Zhongyuan. "A micropower low-noise monolithic instrumentation amplifier for medical purposes". IEEE Journal of Solid State Circuits. 22(6), 1987.

- 9 MA Smither, DR Pugh and LM Woolard. "C.M.R.R. analysis of the 3-op-amp instrumentation amplifier". Electronic Letters. 1997; 13(20): 586.

- 10 Goldhaber-Gordon, D. et. al. Overview of Nanoelectronic Devices. 1997. Proceedings of The IEEE. 85(4): 521-540.

- 11 K. Bult and G Geelen, "A fast-settling CMOS op amps for SC circuits with 90-dB DC gain", IEEE Journal of Solid-State Circuits, Vol. 25, No. 6, Dec. 1990, p.1379-1384.

- 12 B.Y. Kamath, R. G Meyer and P. R. Gray, "Relationship Between Frequency Response and Settling Time of Operational Amplifiers", IEEE Journal of Solid-State Circuits, Vol. SC-9, No. 6, Dec. 1974, p. 347-352.

- 13 Mrinal Das, "Improved Design Criteria of Gain- Boosted CMOS OTA with High-Speed Optimizations", IEEE Trans. on Circuits and Systems II Vol. 49, No. 3, March 2002, p. 204-207.

- 14 K. Bult and G Geelen, "The CMOS gain-boosting technique", Analog Integrated Circuits and Signal Processing, Vol. 1, No. 2, Oct. 1991, p. 119-135.

- 15 European Industry Association (EICTA) MBRAI-02- 16 v1.0 (2004-01): "Mobile and Portable DVB –T Radio Access Interface Specification", 2004.

- 16. P. Bogner, "A 28mW 10b 80MS/s pipelined ADC in0.13μm CMOS", Proc. ISCAS'04, vol. 1, pp. 17-20,2004.