# International Journal Of Advance Research, Ideas And Innovations In Technology

ISSN: 2454-132X Impact factor: 4.295 (Volume3, Issue1)

(Volume3, Issue1)

Available online at: www.ijariit.com

# Simulation Study of Low Power Comparator for A-D Converter

# Dr. M. Nizamuudin

Assistant Professor, ECE Deptt. BGSB University, Rajouri, J&K nizamdelhi25@gmail.com

Abstract- Analog-to-Digital Converters (ADCs) translate the analog quantities into digital language, used in information processing, computing, data transmission and control systems. ADCs are key components for the design of power limited systems, in order to keep the power consumption as low as possible. Implantable Medical electronics, such as Pacemakers and cardiac defibrillators are typical examples of devices where ultra-low-power consumption is paramount. This paper presents design of CMOS comparator based on a preamplifier circuit. Design is intended to be implemented in for Analog-to-Digital Converter (ADC). The design is simulated in 1 µm CMOS Technology with HSPICE. Proposed design exhibits low power consumption. Simulation results are presented and the design has DC Gain of 68dB, power dissipation of 1.25 mW at 5 V.

Keywords-CMOS Comparator, Low Power, High Speed, ADC and HSPICE.

### I. INTRODUCTION

This paper presents design of CMOS comparator based on a preamplifier circuit. Design is intended to be implemented in Analog-to-Digital Converter (ADC). In the A/D conversion process, it is necessary to first sample the input. This sampled signal is than applied to a combination of comparators to determine the digital equivalent of the analog signal [1] and it compare the analog signal with another reference signal and outputs are binary signal based on the comparison. Low power and high speed ADCs are the main building blocks in the front-end of a radio-frequency receiver in most of the modem telecommunication systems. As the comparator is one of the block which limits the speed of the converter, its optimization is of utmost importance. The preamplifier stage amplifies the input signal to improve the comparator sensitivity and isolate the input of the comparator from switching noise coming from positive feedback stage [2]. The latch stage is used to determine which of the input signals is larger and extremely amplifies their difference. The out-put buffer amplifies the information from latch and out-puts a digital signal [3]. One of the critical parts of an ADC greatly influenced by the process variation and mismatch is the comparator. In some ADCs, the offset voltage can be tolerated [4-5].

The comparator is an essential part in the SAR ADC to perform the binary search algorithm. Comparator in the SAR ADC takes more power consumption than the other blocks. A comparator generates a logic output high or low based on the comparison of the analog input with a reference voltage. In an ideal comparator, with infinite gain, for input voltages higher than the reference voltage, the comparator outputs logical one and for the input voltages lower than the reference voltage it produces zero at the output. [5-11].

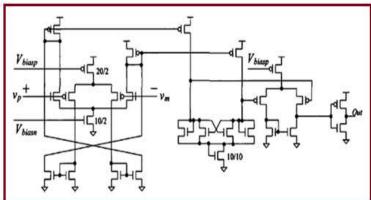

Figure 1- Proposed Comparator

# **Analysis of the Proposed Comparator**

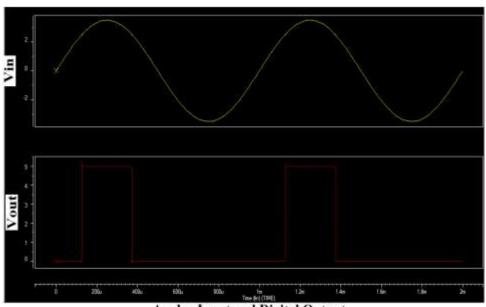

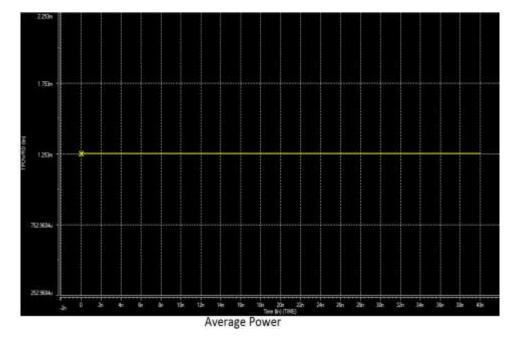

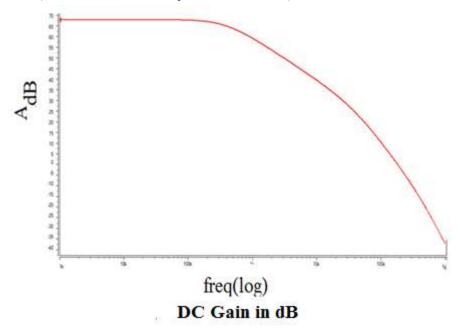

Simulation results are presented and the design has DC Gain of 68dB, power dissipation of 1.25 mW at 5 V. In Transient Analysis input pulse is applied to obtain the desired output apart from AC Analysis to cheek the overall performance of the comparator. The performance limiting blocks in ADCs are typically inter-stage gain amplifiers and comparators. The accuracy of comparators, which is defined by its offset, along with power consumption, speed is of keen interest in achieving overall higher performance of ADCs. To reduce the power consumption and the area of comparators, dynamic comparators are proposed.

### II. SIMULATION RESULTS

Analog Input and Digital Output

## **CONCLUSION**

This paper presents a method for design of CMOS comparator based on a preamplifier. Design is intended to be implemented in Analog-to-Digital Converter (ADC). Simulation results are presented and the design has DC Gain of 68dB, power dissipation of 1.25 mW at 5 V using HSPICE software.

#### REFERENCES

- [1] B. Razavi, "Deign of Analog CMOS Integrated Circuits," Tata McGraw-Hill, Delhi, 2002.

- [2] R. Wang, K. Li, J. Zhang and B. Nie, "A High Speed High Resolution Latch Comparator For-Pipeline ADC," IEEE International Workshop on Anti-counterfeiting, Security, Identification, Xiamen, 16-18 April 2007, pp. 28-31.

- [3] W. Rong, W. Xiaobo and Y. Xiaolang, "A Dynamic CMOS Comparator with High Precision and Resolution," IEEE Proceedings of 7th International Conference on So-lid-State and Integrated Circuits Technology, 18-21 October 2004, pp.

- [4] B. Razavi, B. Wooley, Design techniques for high-speed, high-resolution comparators, IEEE J.Solid-State Circuits 27(12)(1992)1916–1926,

- [5] M. Hati, T.Bhattacharyya, Design of low power parallel pipeline adc in 180nm standard cmos process, in: International Conference on Communications and Signal Processing (ICCSP), 2011, 2011, pp.9–13.

- [6]Bang-Sup Song, Seung-Hoon Lee and Michael F. Tempsett "A 10-b 15- MHz CMOS Recycling Two-step A/D Converter" IEEE Journal of Solid- State Circuits, vol. 25, no. 6, December 1990.

- [7] Amalan Nag, K. L. Baishnab F. A. Talukdar,"Low Power, High Precision and Reduced Size CMOS Comparator for High Speed ADC Design" 2010 5th International Conference on Industrial and Information Systems, ICIIS 2010, Jul 29 Aug 01, 2010, India.

- [8]David J. Allstot "A Precision Variable-Supply CMOS Comparator", IEEE Journal of Solid State Circuits, vol.sc- 17, no.6, Dec.1982.

- [9] Rudy van de Plassche, "CMOS Integrated Analog-to-Digital and Digital-to-Analog Converters" 2nd Edition, Springer International Edition.

- [10] John F. Wakerly, "Digital Design Principles and Practices", 3rd Edition, Pearson Education.

- [11] Douglas A.Pucknell & Kamran Eshraghian, "Basic VLSI Design", 3rd Edition, Prentice Hall of India Pvt.Ltd.